I vårt daglige liv kommer vi over forskjellige typer elektroniske dingser. En av teknologiene som førte til en revolusjon i produksjonen av elektronikk er “ Integrert krets “. Denne teknologien reduserte størrelsen på elektroniske produkter ved å øke tettheten av logiske porter per brikke. I dag har vi forskjellige typer og konfigurasjoner av IC-er. Som vi observerer rundt, finner vi at noen IC-er bare kan brukes til en bestemt applikasjon, mens noen IC-er kan omprogrammeres og brukes til forskjellige applikasjoner. Disse typene IC-er kalles ASIC-er. Men hvordan skiller de seg? Hvordan er det mulig å omprogrammere dem? Hvorfor kan ikke noen IC-er programmeres om? Hopp videre for å finne svar på disse spørsmålene.

Hva er en ASIC (Application Specific Integrated Circuit)?

ASIC fullform er Applikasjonsspesifikk integrert krets. Disse kretsene er applikasjonsspesifikke, dvs. skreddersydde ICer for en bestemt applikasjon. Disse er vanligvis designet fra rotnivå basert på kravet til den aktuelle applikasjonen. Noen av de grunnleggende applikasjonsspesifikke integrerte kretseksempler er sjetonger som brukes i leker, brikken som brukes til grensesnitt mellom minne og mikroprosessor osv ... Disse sjetongene kan bare brukes til den ene applikasjonen som disse er designet for. Antagelig disse typer ICer foretrekkes bare for de produktene som har et stort produksjonsløp. Ettersom ASIC-er er designet fra rotnivået, har de høye kostnader og anbefales bare for produksjoner med høyt volum.

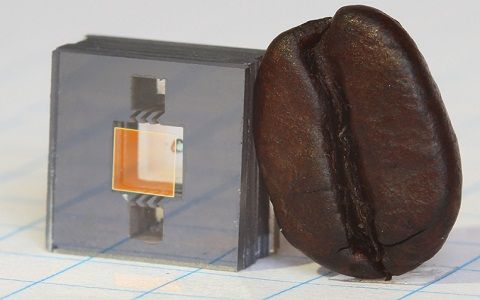

Den største fordelen med ASIC er redusert chipstørrelse ettersom et stort antall funksjonelle enheter i en krets er konstruert over en enkelt chip. Moderne ASIC inkluderer vanligvis en 32-bit mikroprosessor , minneblokker, nettverkskretser osv ... En slik type ASIC er kjent som System on Chip . Med utviklingen i produksjonsteknologi og økt forskning innen designmetoder utvikles ASIC-er med forskjellige nivåer av tilpasning.

Typer ASIC

ASIC-er kategoriseres basert på mengden tilpasning en programmerer har lov til å gjøre på en brikke.

Typer ASIC

Full tilpasset

I denne typen design er alle logiske celler skreddersydd for spesifikke applikasjoner, dvs. designeren må lage logikkcellene for kretsene spesielt. Alle maskelagene for samtrafikk er tilpasset. Så programmerer kan ikke endre sammenkoblinger av brikken, og mens han programmerer, må han være oppmerksom på kretsoppsettet.

Et av de beste eksemplene på full tilpasset ASIC er en mikroprosessor. Denne typen tilpasning lar designere bygge forskjellige analoge kretser, optimaliserte minneceller eller mekaniske strukturer på en enkelt IC. Denne ASIC er kostbar og veldig tidkrevende å produsere og designe. Det tar tid å designe disse IC-ene er rundt åtte uker.

Disse er vanligvis ment for applikasjoner på høyt nivå. Maksimal ytelse, minimert areal og høyeste grad av fleksibilitet er hovedtrekk ved full tilpasset design. Til slutt er risikoen høy i utformingen ettersom logiske celler, motstand osv ... kretselementer som brukes ikke blir prøvetestet.

Semi-tilpasset

I denne typen design er logiske celler hentet fra standardbiblioteker, dvs. de er ikke håndlaget som i Full tilpasset design. Noen masker er tilpasset mens noen er hentet fra det forhåndsdesignede biblioteket. Basert på typen logiske celler hentet fra biblioteket og mengden tilpasning som er tillatt for sammenkoblinger, er disse ASICene delt inn i to typer - Standard cellebasert ASIC og Gate Array-basert ASIC.

1). Standard cellebasert ASIC

For å kjenne disse IC først, la oss forstå hva et standard cellebibliotek står for. Noen av de logiske cellene som f.eks OG porter, ELLER porter , multipleksere, flip-flops er forhåndsdesignet av designere som bruker forskjellige konfigurasjoner, standardiseres og lagres i form av et bibliotek. Denne samlingen er kjent som standard cellebibliotek.

Standard cellebasert ASIC

I standard cellebaserte brukes ASIC-logikkceller fra disse standardbibliotekene. På ASIC-brikken består celleområdet eller den fleksible blokken av standardceller arrangert i form av rader. Sammen med disse fleksible blokkene brukes mega-celler som mikrokontrollere eller til og med mikroprosessorer på brikken. Disse megacellene er også kjent som megafunksjoner, systemnivåmakroer, faste blokker, funksjonelle standardblokker.

Ovenfor figuren representerer en standardcelle-ASIC med et enkelt standardcelleområde og fire faste blokker. Maskelag er tilpasset. Her kan designer plassere standardceller hvor som helst på matrisen. Disse er også kjent som C-BIC.

2). Gate Array Basert ASIC

Denne typen semi-tilpasset ASIC har forhåndsdefinert transistorer på silisiumplaten, dvs. designeren kan ikke endre plasseringen av transistorer som er tilstede på matrisen. Base array er det forhåndsdefinerte mønsteret til gate array, og basecellen er den minste repeterende cellen i basisenheten.

Designeren har kun ansvar for å endre sammenkoblingen mellom transistorer ved hjelp av de første metallagene i formen. Designeren velger fra gate array-biblioteket. Disse kalles ofte som Masked Gate Array. Gate Array Based ASIC er av tre typer. De er Channeled Gate Array, Channel less gate array og en strukturert gate array.

a). Channeled Gate Array

I denne typen gate-array er ledningsrom igjen mellom rader med transistorer. Disse ligner på CBIC ettersom det er igjen plass til sammenkobling mellom blokker, men i kanaliserte gate-array-cellelinjer er faste i høyden, mens dette i CBIC kan justeres.

Channeled Gate Array

Noen av hovedfunksjonene i denne portgruppen er - denne portgruppen bruker forhåndsdefinerte mellomrom mellom rader for samtrafikk. Produksjonstiden er to dager til to uker.

b). Channel Less Gate Array

Det er ikke ledig plass igjen for ruting mellom cellerader, sett i den kanaliserte gateoppstillingen. Her gjøres ruting ovenfra portmatrisecellene, ettersom vi kan tilpasse forbindelsen mellom metall 1 og transistorer. For ruting lar vi transistorer ligge i veien for ruting ubrukt. Produksjonstiden er omtrent to uker.

Channel Less Gate Array

c). Structured Gate Array

Denne typen gate array har en innebygd blokk sammen med gate array rader som vist ovenfor. Strukturert gate-array har en høyere arealeffektivitet på CBIC. I likhet med Masked gate array har disse lavere kostnader og raskere behandlingstid. Her utgjør den faste størrelsen på den innebygde funksjonen en begrensning på det strukturerte gate-arrayet. For eksempel, inneholder denne gate-arrayen et område reservert for 32k bit-kontroller, men hvis vi i en applikasjon bare krever et område for 16k-bit-controller, blir det gjenværende området bortkastet. Alt gate-arrayet har en behandlingstid på to dager til to uker alle har tilpasset samtrafikk.

Structured Gate Array

Programmerbar ASIC

Det er to typer programmerbare ASIC-er. De er PLD og FPGA

PLD-er (programmerbare logiske enheter)

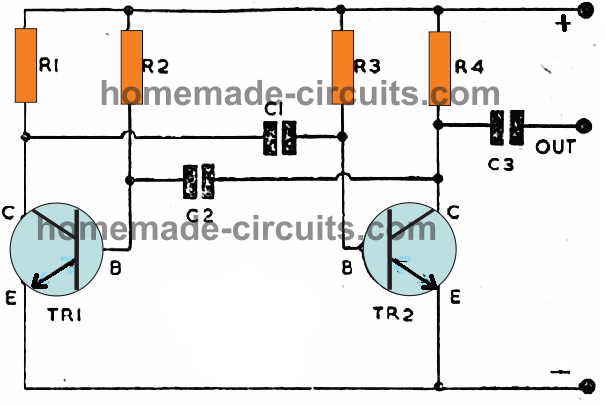

Dette er standardcellene som er lett tilgjengelige. Vi kan programmere en PLD for å tilpasse en del av applikasjonen, slik at de betraktes som ASIC. Vi kan bruke forskjellige metoder og programvare for å programmere en PLD. Disse inneholder en vanlig matrise av logiske celler, vanligvis programmerbar array-logikk sammen med flip-flops eller låser. Her er sammenkoblinger tilstede som en enkelt stor blokk.

PROM er et vanlig eksempel på denne IC. EPROM bruker MOS-transistorer som sammenkobling, så ved å bruke høyspenning kan vi programmere den. PLD har ingen tilpassede logiske celler eller sammenkobling. Disse har en rask designomslag.

Programmerbare logiske enheter

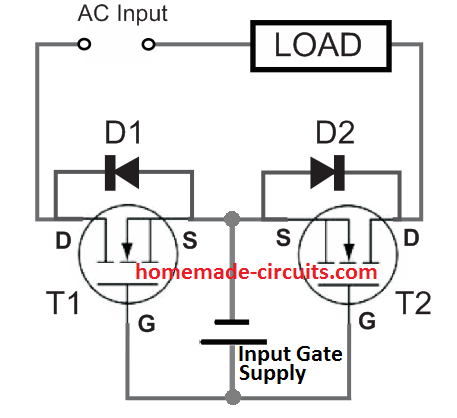

FPGAer (feltprogrammerbar gate matrise)

Hvor PLD har programmerbar matrikklogikk som logiske celler FPGA har gate array-lignende arrangement. PLD er mindre og mindre komplekse enn FPGAer. På grunn av sin fleksibilitet og egenskaper erstatter FPGA TTL i mikroelektroniske systemer. Designomslag er bare noen få timer.

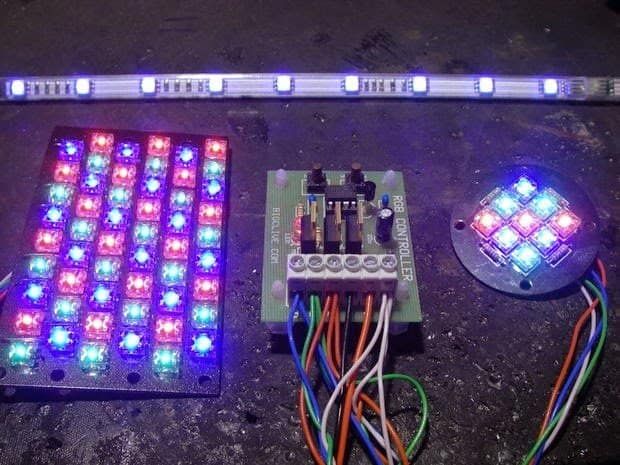

Feltprogrammerbar portarray

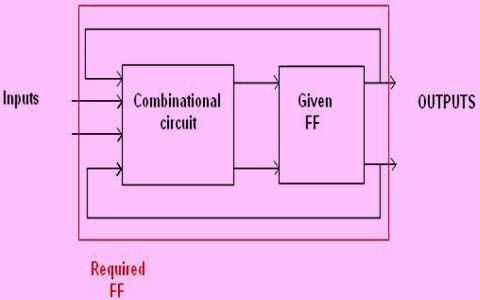

Kjernen består av programmerbare grunnleggende logiske celler som kan utføre begge deler kombinasjons- og sekvensiell logikk . Vi kan programmere logiske celler og koble sammen ved hjelp av noen metoder. Grunnleggende logiske celler er omgitt av matrisen til programmerbare sammenkoblinger, og kjernen er omgitt av programmerbare I / O-celler.

FPGA består vanligvis av konfigurerbare logiske blokker, konfigurerbare I / O-blokker, programmerbare sammenkoblinger, klokkekretser, ALU, minne, dekodere.

Vi har sett de forskjellige typene av ASIC tilgjengelig. La oss nå forstå når alle disse tilpasningene og sammenkoblingene er gjort under produksjonen.

Application Flow for spesifikke integrerte kretsløp (ASIC)

Design av en ASIC utføres trinnvis. Denne rekkefølgen av trinn er kjent som ASIC Design Strømme. Trinn for designflyt er gitt i flytskjemaet nedenfor.

ASIC Design Flow

Designoppføring: På dette trinnet implementeres mikroarkitekturen i designet ved hjelp av maskinvarebeskrivelsesspråk som VHDL, Verilog og System Verilog.

Logisk syntese: På dette trinnet utarbeides en nettliste med logiske celler som skal brukes, typer sammenkoblinger og alle andre deler som kreves for applikasjonen ved hjelp av HDL.

Systempartisjonering: På dette trinnet deler vi den store størrelsen i ASIC-størrelse.

Pre-Layout Simulation: På dette trinnet utføres en simuleringstest for å kontrollere om designet inneholder noen feil.

Gulvplanlegging: På dette trinnet er blokker av netlist arrangert på brikken.

Plassering: På dette trinnet bestemmes plasseringen av celler inne i blokken.

Rute: På dette trinnet trekkes forbindelser mellom blokker og celler. Ekstraksjon: På dette trinnet bestemmer vi de elektriske egenskapene som motstandsverdi og kapasitansverdi for sammenkobling.

Etter-layout-simulering: Før innleveringen av modellen for produksjon blir denne simuleringen gjort for å sjekke om systemet fungerer som det skal sammen med en mengde sammenkobling.

Eksempler på ASIC

Etter å ha kjent de forskjellige egenskapene til ASIC, la oss nå se noen eksempler på ASIC.

Standard cellebasert ASIC: LCB 300k, 500k fra LSI Logic Company, SIG1, 2, 3 familier fra ABB Hafo Inc., GCS90K fra GCS Plessey.

Gate Array-produkter: AUA20K fra Harris Semiconductor, SCX6Bxx fra National Semiconductors, TGC / TEC-familier fra Texas Instruments.

PLD-produkter: PAL-familie av avanserte mikroenheter, GAL-familien fra Philips Semiconductors, XC7300 og EPLD fra XILINX.

FPGA-produkter: XC2000, XC3000, XC4000, XC5000-serien fra XILINX, pASIC1 fra QuickLogic, MAX5000 fra Altera.

Søknader om ASIC

Det unike med ASIC har revolusjonert måten elektronikk produseres på. Disse reduserte formstørrelsene mens de økte tettheten av logiske porter per brikke. ASIC-er foretrekkes vanligvis for applikasjoner på høyt nivå. ASIC-brikke brukes som IP-kjerner for satellitter, ROM-produksjon, Mikrokontroller og ulike typer applikasjoner innen medisin og forskning. En av de populære applikasjonene til ASIC er BITCOIN MINER.

Bitcoin Miner

Gruvedrift av kryptovaluta krever større kraft og høyhastighets maskinvare. En generell CPU kan ikke gi en så høyere databehandlingskapasitet i høy hastighet. ASIC bitcoin minearbeidere er chips innebygd i spesialdesignede hovedkort og strømforsyninger , konstruert i en enkelt enhet. Det er en målrettet designet maskinvare helt ned til chipnivået for bitcoin mining. Disse enhetene kan utføre algoritmen til bare enkelt kryptovaluta. For en annen type kryptokurrency antagelig trenger vi en annen gruvearbeider.

Fordeler og ulemper ved ASIC

De fordelene med ASIC Inkluder følgende.

- Den lille størrelsen på ASIC gjør det til et høyt valg for sofistikerte større systemer.

- Siden et stort antall kretser er bygd over en enkelt brikke, forårsaker dette applikasjoner med høy hastighet.

- ASIC har lavt strømforbruk.

- Siden de er systemet på brikken, er kretser tilstede side om side. Så det kreves veldig minimal ruting for å koble til forskjellige kretser.

- ASIC har ingen timingproblemer og konfigurasjon etter produksjon.

De ulemper med ASIC Inkluder følgende.

- Ettersom dette er tilpassede sjetonger, gir de liten fleksibilitet for programmering.

- Ettersom disse sjetongene må utformes fra rotnivået, koster de per enhet.

- ASIC har større tid til markedsmargin.

ASIC vs FPGA

Forskjellen mellom ASIC og FPGA inkluderer følgende.

ASIC | FPGA |

| Ikke omprogrammerbar | Omprogrammerbar |

| Foretrukket for produksjoner med høyt volum | Foretrukket for produksjoner med lite volum |

| Disse er applikasjonsspesifikke | Brukes som prototyper av et system |

| Energieffektiv krever mindre strøm | Mindre energieffektiv krever mer kraft |

| Dette er permanente kretsløp som ikke kan oppgraderes fra tid til annen. | Svært egnet for applikasjoner der kretsen må oppgraderes fra tid til annen, for eksempel mobiltelefonbrikker, basestasjoner osv |

Dermed handler alt om en oversikt over Applikasjonsspesifikk integrert krets . Oppfinnelsen av ASIC har forårsaket en enorm endring i måten elektronikk brukes på. Vi bruker ASIC i vårt daglige liv i form av forskjellige applikasjoner. Hvilke applikasjoner av ASIC har du kommet over? Hvilken type ASIC har du jobbet med?