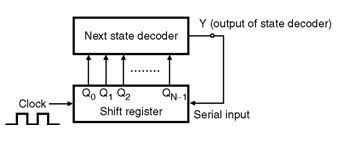

I digital elektronikk er skiftregistre de sekvensielle logiske kretsene som kan lagre dataene midlertidig og gir dataoverføringen mot utgangsenheten for hver klokkepuls. Disse er i stand til å overføre / forskyve dataene enten mot høyre eller venstre i seriell og parallell modus. Basert på modusen for inngangs- / utgangsoperasjoner, kan skiftregister brukes som et seriell-parallell-ut-skiftregister, seriell-i-seriell-ut skiftregister , parallell-i-parallell-ut skiftregister, parallell-i-parallell-ut skiftregister. Basert på forskyvning av data, finnes det universelle skiftregistre og toveis skiftregister. Her er en komplett beskrivelse av det universelle skiftregisteret.

Hva er et Universal Shift Register?

Definisjon: Et register som kan lagre dataene og / forskyver dataene mot høyre og venstre sammen med den parallelle belastningsevnen, er kjent som et universalt skiftregister. Den kan brukes til å utføre inngangs- / utgangsoperasjoner i både seriell og parallell modus. Enveis skift registre og toveis skiftregister kombineres for å få utformingen av det universelle skiftregisteret. Det er også kjent som et parallell-inn-parallelt-ut skiftregister eller skiftregister med parallell belastning.

Universalskiftregister kan utføre tre operasjoner som listet opp nedenfor.

- Parallell belastning - lagrer dataene parallelt så vel som dataene parallelt

- Skift venstre operasjon - lagrer dataene og overfører dataene som skifter mot venstre i den serielle banen

- Skift høyre betjening - lagrer dataene og overfører dataene ved å skifte mot høyre i seriebanen.

Derfor kan universelle skiftregistre utføre inngangs- / utgangsoperasjoner med både seriell og parallell belastning.

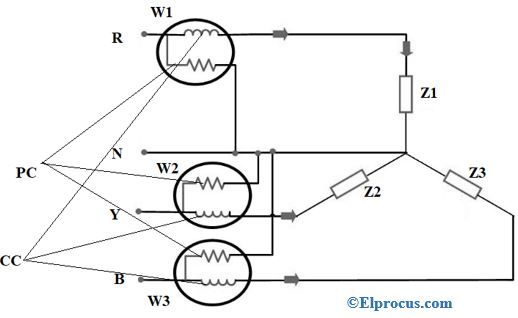

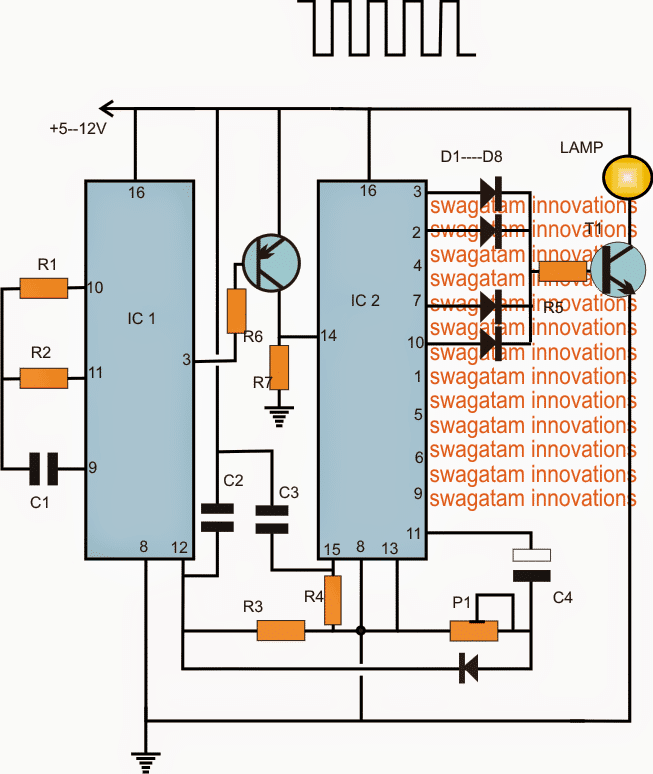

Diagram over universalt skiftregister

4-biters universalt skiftregisterdiagram er vist nedenfor.

Diagram over universalt skiftregister

- Seriell inngang for skift-høyre kontroll muliggjør dataoverføring mot høyre, og alle serielle inngangs- og utgangslinjene er koblet til skift-høyre-modus. Inngangen blir gitt til AND-porten-1 på flip-flop -1 som vist på figuren via seriell inngangsstift.

- Seriell inngang for skift-venstre muliggjør dataoverføring mot venstre, og alle serielle inngangs- og utgangslinjene er koblet til skift-venstre-modus.

- I parallell dataoverføring er alle parallelle innganger og utgangslinjer tilknyttet parallell belastning.

- Clear pin tømmer registeret og settes til 0.

- CLK-pin gir klokkepulser for å synkronisere alle operasjoner.

- I kontrolltilstand vil ikke informasjonen eller dataene i registeret endres selv om klokkepulsen påføres.

- Hvis registeret opererer med en parallell belastning og forskyver dataene mot høyre og venstre, fungerer det som et universalt skiftregister.

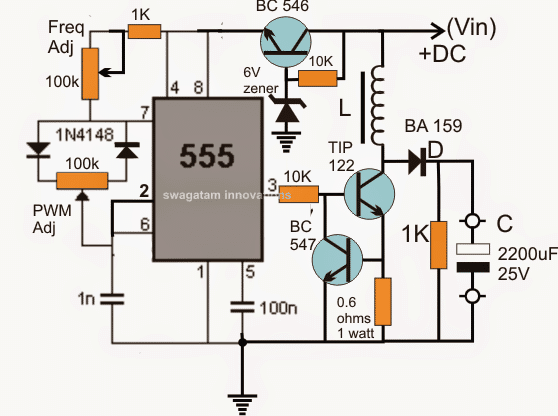

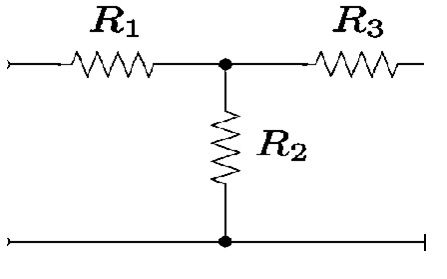

Design av Universal Shift Register

Utformingen av et 4-biters universalt skiftregister ved hjelp av multipleksere og flip-flops er vist nedenfor.

Universal Shift Register Design

- S0 og S1 er de valgte pinnene som brukes til å velge modus for dette registeret. Det kan være skift til venstre eller skift til høyre eller parallell modus.

- Pin-0 av første 4 × 1 Mux blir matet til utgangspinnen til den første flip-flop. Observer tilkoblingene som vist på figuren.

- Pin-1 til den første 4X1 MUX er koblet til seriell inngang for skift til høyre. I denne modusen forskyver registeret dataene mot høyre.

- På samme måte er pin-2 på 4X1 MUX koblet til den serielle inngangen for shift-venstre. I denne modusen forskyver det universelle skiftregisteret dataene mot venstre.

- M1 er de parallelle inngangsdata gitt til pin-3 i den første 4 × 1 MUX for å gi parallellmodusoperasjon og lagrer dataene i registeret.

- Tilsvarende blir gjenværende individuelle parallelle inngangsbiter gitt til pin-3 til relatert 4X1MUX for å gi parallell belastning.

- F1, F2, F3 og F4 er de parallelle utgangene til Flip-flops, som er assosiert med 4 × 1 MUX.

Universal Shift Register fungerer

- Fra figuren ovenfor, valgte markerer driftsmåten til universalskiftregisteret. Seriell inngang forskyver dataene mot høyre og venstre og lagrer dataene i registeret.

- Clear pin og CLK pin er koblet til flip-flop.

- M0, M1, M2, M3 er parallelle innganger mens F0, F1, F2, F3 er parallelle utganger fra flip-flops

- Når inngangspinnen er aktiv HØY, laster / henter inn universalskiftregisteret dataene parallelt. I dette tilfellet er inngangspinnen direkte koblet til 4 × 1 MUX

- Når inngangspinnen (modus) er aktiv LAV, forskyver universalskiftregisteret dataene. I dette tilfellet er inngangspinnen koblet til 4 × 1 MUX via NOT gate.

- Når inngangspinnen (modus) er koblet til GND (Ground), fungerer universalskiftregisteret som et toveis skiftregister.

- For å utføre skift-høyre-operasjonen, mates inngangspinnen til den første OG-porten til den første flip-flop via seriell inngang for shit-right.

- For å utføre skift-venstre-operasjonen mates inngangspinnen til den 8. OG-porten til den siste flip-flop via inngang M.

- Hvis de valgte pinnene S0 = 0 og S1 = 0, fungerer ikke dette registeret i noen modus. Det betyr at den vil være i låst tilstand eller ingen endringsstatus selv om klokkepulsene blir brukt.

- Hvis de valgte pinnene S0 = 0 og S1 = 1, overfører eller skifter dette registeret dataene til venstre og lagrer dataene.

- Hvis de valgte pinnene S0 = 1 og S1 = 0, forskyver dette registeret dataene til høyre og utfører dermed skift-høyre-operasjonen.

- Hvis de valgte pinnene S0 = 1 og S1 = 1, laster dette registeret dataene parallelt. Derfor utfører den parallell lasting og lagrer dataene.

S0 | S1 | Driftsmåte |

0 | 0 | Låst tilstand (ingen endring) |

0 | 1 | Skift-Venstre |

| 1 | 0 | Skift-Høyre |

| 1 | 1 | Parallell lasting |

Fra tabellen ovenfor kan vi observere at dette registeret fungerer i alle moduser med serielle / parallelle innganger ved bruk av 4 × 1 multiplexere og flip-flops.

Fordeler

De fordelene med et universalt skiftregister Inkluder følgende.

- Dette registeret kan utføre tre operasjoner som skift til venstre, skift til høyre og parallell belastning.

- Lagrer dataene midlertidig med i registeret.

- Den kan utføre seriell til parallell, parallell med seriell, parallell med parallell og seriell til seriell operasjon.

- Den kan utføre inngangs- og utgangsoperasjoner i både modiene serielle og parallelle.

- En kombinasjon av ensrettet skiftregister og toveis skiftregister gir universets skiftregister.

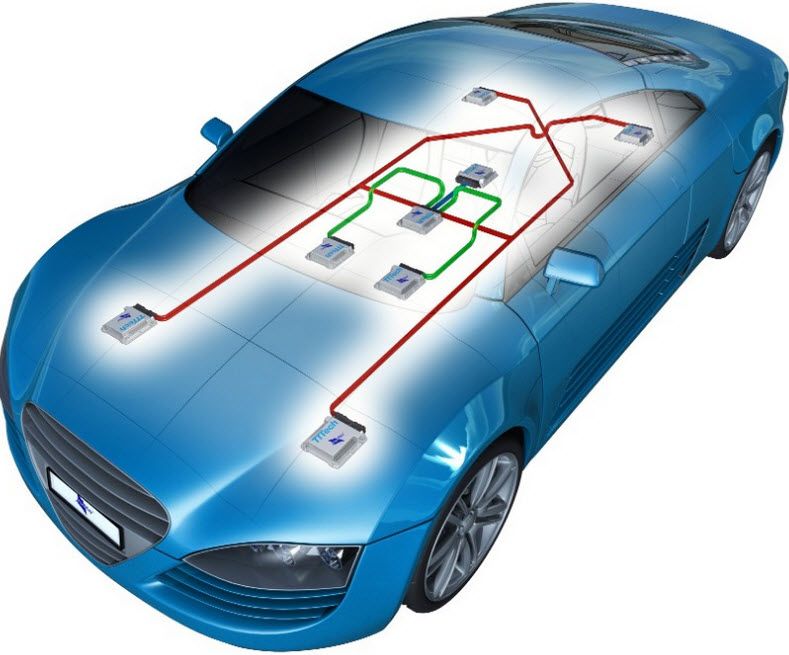

- Dette registeret fungerer som et grensesnitt mellom en enhet til en annen enhet for å overføre dataene.

applikasjoner

De anvendelser av et universalt skiftregister Inkluder følgende.

- Brukt i mikrokontroller for I / O-utvidelse

- Brukes som en seriell-til-seriell omformer

- Brukes som en parallell-til-parallell datakonverterer

- Brukes som en seriell-til-parallell datakonverterer.

- Brukes i seriell til seriell dataoverføring

- Brukes i parallell dataoverføring.

- Brukes som et minneelement i digital elektronikk som datamaskiner.

- Brukes i applikasjoner med tidsforsinkelse

- Brukes som frekvens tellere, binære tellere og digitale klokker

- Brukes i datamanipuleringsapplikasjoner.

Dermed handler dette om det universelle skiftregister - definisjon , diagram, design, arbeid, fordeler og ulemper. Det finnes forskjellige typer 4-bits registre som er tilgjengelige i form av IC 74291, IC 74395 og mange flere. Her er et spørsmål til deg, 'Hva fungerer det toveis universelle skiftregisteret?'