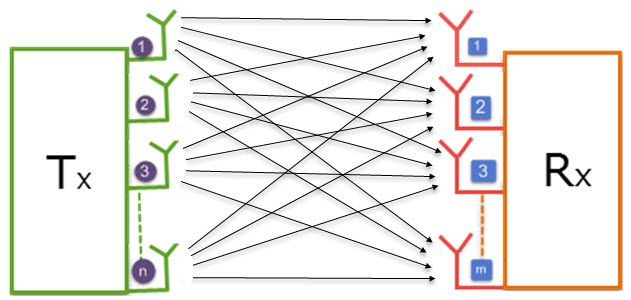

I kombinasjonskretsene brukes forskjellige logiske porter til å designe koder, multiplekser, dekoder og de-multiplexer. Disse kretsene har noen egenskaper som utgangen til denne kretsen avhenger hovedsakelig av nivåene som er der på inngangsterminalene når som helst. Denne kretsen inkluderer ikke noe minne. Den tidligere tilstanden til inngangen har ingen innflytelse på den nåværende tilstanden til denne kretsen. Inngangene og utgangene til en kombinasjonskrets er ‘n’ nr. av innganger & ‘m’ nr. av utganger. Noen av kombinasjonskretsene er halv adder og full adder, subtraktor, koder, dekoder, multiplexer og demultiplexer. Denne artikkelen diskuterer en oversikt over halvtall og fulladder, og det fungerer med sannhetstabeller.

Hva er en Adder?

En hugger er en digital logikkrets i elektronikk som er mye brukt for å legge til tall. I mange datamaskiner og andre typer prosessorer brukes tilsetninger til og med til å beregne adresser og relaterte aktiviteter og beregne tabellindekser i ALU og til og med brukt i andre deler av prosessorer. Disse kan bygges for mange numeriske representasjoner som overskudd-3 eller binær kodet desimal. Tilleggere er i utgangspunktet klassifisert i to typer: Half Adder og Full Adder.

Hva er Half Adder and Full Adder Circuit?

Halvadderkretsen har to innganger: A og B, som legger til to inngangssifre og genererer en bære og en sum. Hele adderkretsen har tre innganger: A og C, som legger til tre inngangstall og genererer en bære- og sum. Denne artikkelen gir detaljert informasjon om hva som er formålet med en halvhugg og full adder i tabellform og til og med i kretsskjemaer også. Det er allerede nevnt at det viktigste og avgjørende formålet med addere er addisjon. Nedenfor er detaljene halv hugger og full hugger teori.

Grunnleggende halvadder og fulladder

Halvadder

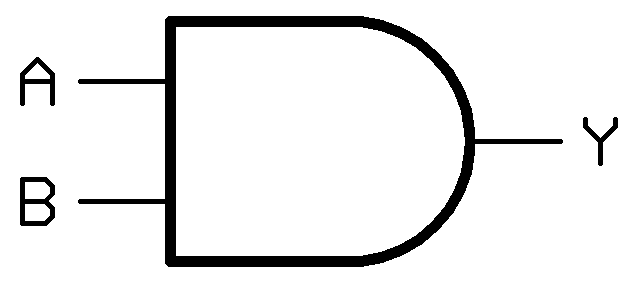

Så når vi kommer til scenariet med halv adder, legger det til to binære sifre der inngangsbitene blir betegnet som augend og addend, og resultatet blir to utganger, den ene er summen og den andre er bære. For å utføre sumoperasjonen blir XOR brukt på begge inngangene, og AND-gate brukes på begge inngangene for å produsere bære.

HA Funksjonsdiagram

Mens det i den fullstendige adderkretsen legges til 3 ett-bits tall, hvor to av de tre bitene kan betegnes som operander, og den andre betegnes som bit som er innført. Den produserte utgangen er 2-bits utgang og disse kan henvises til som output carry and sum.

Ved å bruke en halv adder kan du designe enkelt tillegg ved hjelp av logiske porter.

La oss se et eksempel på å legge til to enkeltbiter.

2-bit halvt adder sannhetsbord er som nedenfor:

Sannhetstabell for halv adder

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Dette er minst mulig kombinasjon av enkeltbiter. Men resultatet for 1 + 1 er 10, sumresultatet må skrives om som en 2-bits utgang. Dermed kan ligningene skrives som

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Utgangen '1'of' 10 'er gjennomføring. 'SUM' er normal utgang og 'CARRY' er gjennomføring.

Nå er det blitt ryddet at en 1-biters adder lett kan implementeres ved hjelp av XOR-porten for utgangen ‘SUM’ og en OG-port for ‘Carry’.

For eksempel, når vi trenger å legge til, to 8-biters byte sammen, så kan den implementeres ved hjelp av en fulladder-logikkrets. Halvadderet er nyttig når du vil legge til ett binært siffer.

En måte å utvikle to-binære siffer adders på ville være å lage en sannhetstabell og redusere den. Når du vil lage en tre binærsifret adder, utføres den halve addertilleggsoperasjonen to ganger. På samme måte, når du bestemmer deg for å lage en firesifret adder, utføres operasjonen en gang til. Med denne teorien var det klart at implementeringen er enkel, men utvikling er en tidskrevende prosess.

Det enkleste uttrykket bruker den eksklusive ELLER-funksjonen:

Sum = A XOR B

Bære = A OG B

HA logisk diagram

Og et tilsvarende uttrykk når det gjelder grunnleggende AND, OR og NOT er:

SUM = A.B + A.B ’

VHDL-kode for halv adder

Enhet ha er

Port (a: i STD_LOGIC

b: i STD_LOGIC

sha: ut STD_LOGIC

cha: ut STD_LOGIC)

slutt ha

Arkitektur Behavioral av ovennevnte krets er

begynne

sha<= a xor b

Nei<= a and b

slutt Atferdsmessig

Halvadder IC-nummer

Implementeringen av halv adder kan gjøres gjennom høyhastighets CMOS digitale logiske integrerte kretser som 74HCxx-serien som inkluderer SN74HC08 (7408) og SN74HC86 (7486).

Begrensninger for halv adder

Hovedårsaken til å kalle disse binære tilleggene som Half Adders er at det ikke er noe område å inkludere bærebiten ved å bruke en tidligere bit. Så dette er en hovedbegrensning av HA som en gang ble brukt som binær adder, spesielt i sanntidssituasjoner som innebærer å legge til flere biter. Så denne begrensningen kan overvinnes ved å bruke de fulle tilleggene.

Full Adder

Denne adderen er vanskelig å implementere når den sammenlignes med half-adder.

Full Adder Functional Diagram

Forskjellen mellom en halv-og en full-adder er at full-adder har tre innganger og to utganger, mens halv adder har bare to innganger og to utganger. De to første inngangene er A og B, og den tredje inngangen er en inngangsbære som C-IN. Når en fulladderlogikk er utformet, strenger du åtte av dem sammen for å lage en byte-bred adder og kaskade bærebiten fra en adder til den neste.

FA sannhetstabell

Utgangsbære er betegnet som C-OUT og normal utgang er representert som S som er 'SUM'.

Med ovennevnte full adder sannhetstabell , kan implementeringen av en full adderkrets lett forstås. SUM ‘S’ er produsert i to trinn:

- Ved å XOR bruke inngangene 'A' og 'B'

- Resultatet av A XOR B blir deretter XORed med C-IN

Dette genererer SUM og C-OUT er bare sant når begge to av tre innganger er HIGH, så vil C-OUT være HIGH. Så vi kan implementere en full adderkrets ved hjelp av to halve adderkretser. Opprinnelig vil den halve adderen brukes til å legge til A og B for å produsere en delvis sum, og en annen halvdel av adderlogikken kan brukes til å legge til C-IN til summen som produseres av første halvdel for å få den endelige S-utgangen.

Hvis noe av halvtalllogikken produserer en bære, vil det være en utgangsbære. Så, C-OUT vil være en ELLER-funksjon av Carry-utgangene til halvt adder. Ta en titt på implementeringen av den fullstendige adderkretsen vist nedenfor.

Full Adder Logical Diagram

Implementeringen av større logiske diagrammer er mulig med ovennevnte fulladderlogikk, og et enklere symbol brukes for det meste for å representere operasjonen. Nedenfor er en enklere skjematisk fremstilling av en en-bit full adder.

Med denne typen symbol kan vi legge til to biter sammen, ta en bære fra neste lavere størrelsesorden og sende en bære til neste høyere størrelsesorden. I en datamaskin, for en flerbitsoperasjon, må hver bit være representert av en full adder og må legges til samtidig. Dermed, for å legge til to 8-bits tall, trenger du 8 fulle addere som kan dannes ved å kaskade to av 4-biters blokkene.

Halvadder og fulladder ved bruk av K-Map

Selv summen og bæreutgangene for halvaddere kan også oppnås med metoden til Karnaugh-kartet (K-map). De halv adder og full adder boolsk uttrykk kan fås gjennom K-map. Så K-kartet for disse tilleggene er diskutert nedenfor.

Halvhuggeren K-map er

HA K-Map

Hele adder K-Map er

FA K-Map

Logisk uttrykk for SUM og Carry

Det logiske uttrykket for sum (S) kan bestemmes ut fra inngangene nevnt i tabellen.

= A’B’Cin + A ’B CCin’ + A B’Cin ’+ AB Cin

= Cin (A’B ’+ AB) + Cin’ (A’B + A B ’)

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Det logiske uttrykket for bæringen (Cout) kan bestemmes ut fra inngangene nevnt i tabellen.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Med de ovennevnte sannhetstabellene kan resultatene oppnås og prosedyren er:

En kombinasjonskrets kombinerer de forskjellige portene i kretsen der de kan være en koder, dekoder, multiplexer og demultiplexer . Egenskapene til kombinasjonskretser er som følger.

- Utgangen når som helst er bare basert på nivåene som er tilstede på inngangsterminalene.

- Det bruker ikke noe minne. Den forrige inngangstilstanden har ingen effekt på kretsens nåværende tilstand.

- Den kan ha et hvilket som helst antall innganger og m antall utganger.

VHDL-koding

VHDL-koding for full adder Inkluder følgende.

enhet full_add er

Port (a: i STD_LOGIC

b: i STD_LOGIC

cin: i STD_LOGIC

sum: ut STD_LOGIC

cout: ut STD_LOGIC)

avslutte full_add

Architecture Behavioral of full_add is

komponent ha er

Port (a: i STD_LOGIC

b: i STD_LOGIC

sha: ut STD_LOGIC

cha: ut STD_LOGIC)

sluttkomponent

signal s_s, c1, c2: STD_LOGIC

begynne

HA1: ha port kart (a, b, s_s, c1)

HA2: ha port kart (s_s, cin, sum, c2)

koste<=c1 or c2

slutt Atferdsmessig

De forskjell mellom halvtall og fulltann er at halvmåler produserer resultater og fullmåler bruker halvmåler for å produsere noe annet resultat. Tilsvarende, mens Full-Adder er av to Half-Adders, er Full-Adder den faktiske blokken vi bruker for å lage de aritmetiske kretsene.

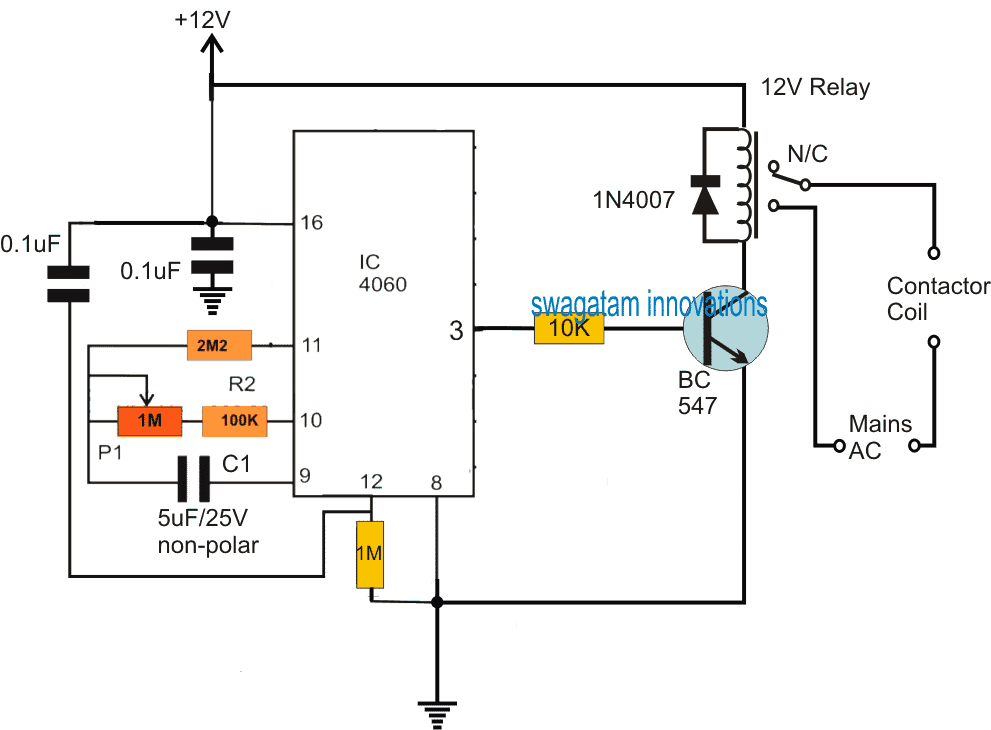

Carry Lookahead Adders

I begrepet krusebæreadderkretser er bitene som er nødvendige for tillegg umiddelbart tilgjengelige. Mens hver adderseksjon trenger å holde tiden for ankomst av bære fra forrige adderblokk. På grunn av dette tar det mer tid å produsere SUM og CARRY ettersom hver seksjon i kretsen venter på ankomst av inngang.

For eksempel, for å levere utgang for den nte blokken, må den motta inngang fra (n-1) blokk. Og denne forsinkelsen blir tilsvarende betegnet som forplantningsforsinkelse.

For å overvinne forsinkelsen i ripple bærer huggorm, ble en bære-lookahead huggorm introdusert. Her, ved å bruke komplisert maskinvare, kan forplantningsforsinkelsen minimeres. Diagrammet nedenfor viser en carry-lookahead-hugger ved hjelp av fulladdere.

Bær Lookahead ved hjelp av fulladder

Sannhetstabellen og tilsvarende utgangsligninger er

| TIL | B | C | C + 1 | Betingelse |

| 0 | 0 | 0 | 0 | Ingen bærer generere |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Ingen bærer Formere |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Bære generere |

| 1 | 1 | 1 | 1 |

Bæreforplantningsligningen er Pi = Ai XOR Bi og bæregenereringen er Gi = Ai * Bi. Med disse ligningene kan sum- og bærelikningene vises som

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi leverer bare når begge inngangene Ai og Bi er 1 uten å ta hensyn til inngangen. Pi er relatert til bæreutbredelsen fra Ci til Ci + 1.

Forskjellen mellom Half Adder og Full Adder

De forskjellen mellom halv- og fulladdertabellen er vist nedenfor.

| Halvadder | Full Adder |

| Half Adder (HA) er en kombinasjonslogisk krets, og denne kretsen brukes til å legge til to en-bits sifre. | Full Adder (FA) er en kombinasjonskrets, og denne kretsen brukes til å legge til tre en-bits sifre. |

| Når HA er generert fra forrige tilføyelse i HA, kan ikke legges til neste trinn. | Når FA er generert fra den tidligere tilsetningen i FA, kan den legges til neste trinn. |

| Half adder inkluderer to logiske porter som AND gate og EX-OR gate. | Full adder inkluderer to EX-ELLER porter, to ELLER porter og to OG porter. |

| Inndatabitene i halvtallsmodellen er to som A, B. | Inndatabitene i fulladderen er tre som A, B & C-in |

| Halvtallssummer og bære ligning er S = a⊕b C = a * b | Full adder logikk uttrykk er S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA brukes i datamaskiner, kalkulatorer, enheter som brukes til digital måling, etc. | FA brukes i digitale prosessorer, multibitstilsetning osv. |

De nøkkelforskjeller mellom halvmåler og fullmåler er diskutert nedenfor.

- Halvadder genererer sum & carry ved å legge til to binære innganger, mens fulladderen brukes til å generere sum & carry ved å legge til tre binære innganger. Både halvadder- og fulladder-maskinvarearkitekturen er ikke den samme.

- Hovedtrekket som skiller HA og FA er at det i HA ikke er noen slik avtale å vurdere det siste tilskuddet som dets innspill. Men, en FA finner en bestemt inndatakolonne som Cin for å vurdere det siste tilskuddets bærebit.

- De to tilsetningene vil vise en forskjell basert på komponentene som brukes i kretsen for konstruksjonen. Half adders (HA) er designet med kombinasjonen av to logiske porter som AND & EX-OR, mens FA er designet med kombinasjonen av tre AND, to XOR og en ELLER porter.

- I utgangspunktet opererer HA på 2-to innganger på 1-bit, mens FA-ene opererer på tre innganger på 1-bit. Half adder brukes i forskjellige elektroniske enheter for å evaluere tillegget, mens full adder brukes i digitale prosessorer for tilsetning av en lang bit.

- Likhetene i disse to tilleggene er, begge HA og FA er kombinasjons digitale kretser, så de bruker ikke noe minneelement som sekvensielle kretser. Disse kretsene er essensielle for aritmetisk drift for å gi tillegg av det binære tallet.

Full Adder Implementation ved hjelp av Half Adders

Implementeringen av en FA kan gjøres gjennom to halv addere som er koblet logisk. Blokkdiagrammet for dette kan vises nedenfor som forteller tilkoblingen av en FA ved hjelp av to halvaddere.

Summen og bære ligningene fra tidligere beregninger er

S = A ‘B’ Cin + A ’BC’ i + ABCin

Cout = AB + ACin + BCin

Sumligningen kan skrives som.

Cin (A’B ‘+ AB) + C‘ in (A‘B + A B ')

Så, Sum = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout kan skrives som følger.

COUT = AB + ACin + BCin.

Coût = AB + + skuffelser BCIN (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ’) + A’ B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Derfor COUT = AB + Cin (A EX-OR B)

Avhengig av de to ovennevnte summene og bære ligningene, kan FA-kretsen implementeres ved hjelp av to HA og en ELLER-port. Kretsskjemaet for en fulladder med to halvaddere er illustrert ovenfor.

Full Adder ved hjelp av to halvaddere

Full Adder Design med bruk av NAND Gates

En NAND-port er en slags universalport, som brukes til å utføre alle slags logiske design. FA-kretsen med NAND-portdiagrammet er vist nedenfor.

FA ved hjelp av NAND Gates

FA er en enkel en-bit-adder, og hvis vi ønsker å utføre tillegg av n-bit, så n nei. av en-bit FA må brukes i kaskadeforbindelsesformatet.

Fordeler

De fordelene med halvhugg og fullhugg Inkluder følgende.

- Det fremste formålet med en halv adder er å legge til to single-bit tall

- Fulladdere har muligheten til å legge til en bærebit som er resultatet av forrige tillegg

- Med full adder kan viktige kretser som adder, multiplexer og mange andre implementeres

- Hele adderkretsene bruker minimalt med strøm

- Fordelene med en fulladder over en halv adder er, en full adder brukes til å overvinne ulempen med en halv adder fordi halv adder hovedsakelig brukes til å legge til to 1-bit tall. Halv addere legger ikke til bærebiten, så for å overvinne denne fulladderen er den ansatt. I Full adder kan tilsetning av tre biter gjøres og genererer to utganger.

- Det er enkelt å utforme tilsetninger, og det er en grunnleggende byggestein slik at en-bitstilsetning lett kan forstås.

- Denne addisjonen kan konverteres til halv subtraktor ved å legge til en inverter.

- Ved å bruke en full adder kan du oppnå høy ytelse.

- Høy hastighet

- Svært sterk forsyningsspenning

Ulemper

De ulemper med halv hugger og full hugger Inkluder følgende.

- I tillegg kan halv adder ikke brukes før bæring, så det er ikke aktuelt for kaskadering av tillegg av multi-bit.

- For å overvinne denne ulempen er FA nødvendig å legge til tre 1 bit.

- Når FA er brukt i form av en kjede som en RA (Ripple Adder), kan stasjonens evne til å reduseres.

applikasjoner

Søknadene om halvt og helt hugger inkluderer følgende.

- Den binære bitetilsetningen kan gjøres ved halv adder ved hjelp av ALU i datamaskinen fordi den bruker adder.

- Half adder kombinasjon kan brukes til å designe en full adder krets.

- Halv addere brukes i kalkulatorene og til å måle adressene samt tabellene

- Disse kretsene brukes til å håndtere forskjellige applikasjoner innen digitale kretser. I fremtiden spiller den en nøkkelrolle i digital elektronikk.

- En FA-krets brukes som et element i mange store kretser som Ripple Carry Adder. Denne adderen legger til antall bits samtidig.

- FA brukes i Arithmetic Logic Unit (ALU)

- FA-er brukes i grafikkrelaterte applikasjoner som GPU (Graphics Processing Unit)

- Disse brukes i multiplikasjonskretsen for å utføre Carryout Multiplikation.

- På en datamaskin, for å generere minneadressen og bygge programkontrapunktet mot etterfølgende instruksjon, brukes Arithmetic Logic Unit ved å bruke Full Adders.

Således, når tillegget av to binære tall er gjort, blir sifrene først lagt til de minste bitene. Denne prosessen kan utføres gjennom en halv adder fordi den enkleste n / w som tillater å legge til to 1-bit tall. Inngangene til denne adderen er de binære sifrene, mens utgangene er summen (S) og bæringen (C).

Når antall sifre er inkludert, blir HA-nettverket bare brukt til å koble til de minste sifrene, da HA ikke kan legge til bære nummer fra den tidligere klassen. En full adder kan defineres som basen til alle digitale aritmetiske enheter. Dette brukes til å legge til tre 1-sifrede tall. Denne adderen inkluderer tre innganger som A, B og Cin mens utgangene er Sum og Cout.

Relaterte konsepter

De begreper relatert til halvtall og fulltann bare ikke hold deg til et eneste formål. De har omfattende bruk i mange applikasjoner, og noen av de relaterte er nevnt:

- Halvadder og fulladder IC-nummer

- Utvikling av 8-biters adder

- Hva er de halve adderforholdsregler?

- JAVA Applet of a Ripple Carry Adder

Derfor handler dette om halv hugger og full hugger teori sammen med sannhetstabellene og logiske diagrammer, vises også utformingen av fulladder ved hjelp av halv adderkrets. Mange av de halv adder og full adder pdf dokumenter er tilgjengelige for å gi avansert informasjon om disse konseptene. Det er videre viktig å vite hvordan en 4-biters fulladder implementeres ?